2024-02-23 03:14:58

2024-02-23 03:14:58 浏览次数:

function tag_arcclick(aid)

{

var ajax = new XMLHttpRequest();

ajax.open("get", "/index.php?m=api&c=Ajax&a=arcclick&aid="+aid+"&type=view", true);

ajax.setRequestHeader("X-Requested-With","XMLHttpRequest");

ajax.setRequestHeader("Content-type","application/x-www-form-urlencoded");

ajax.send();

ajax.onreadystatechange = function () {

if (ajax.readyState==4 && ajax.status==200) {

document.getElementById("eyou_arcclick_1711514935_"+aid).innerHTML = ajax.responseText;

}

}

}

浏览次数:

function tag_arcclick(aid)

{

var ajax = new XMLHttpRequest();

ajax.open("get", "/index.php?m=api&c=Ajax&a=arcclick&aid="+aid+"&type=view", true);

ajax.setRequestHeader("X-Requested-With","XMLHttpRequest");

ajax.setRequestHeader("Content-type","application/x-www-form-urlencoded");

ajax.send();

ajax.onreadystatechange = function () {

if (ajax.readyState==4 && ajax.status==200) {

document.getElementById("eyou_arcclick_1711514935_"+aid).innerHTML = ajax.responseText;

}

}

}

返回列表

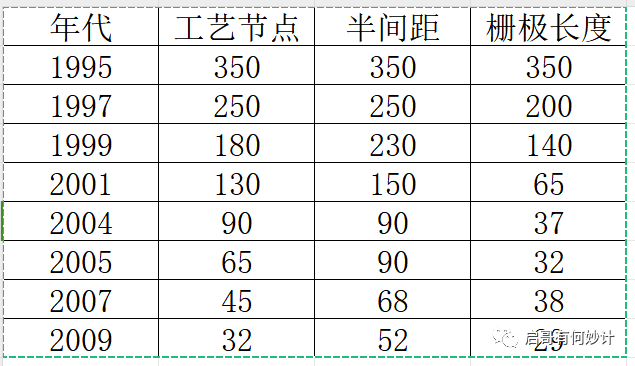

返回列表 实质上权衡晶体管巨细,原来有两个目标,栅长gate length和半间距half pitch。正在350nm到28nm之间,业内定下来,平素通用栅长gate length来指代工艺节点,直到14nm发轫由于情形又有了宏伟的改观,又回到用半间距half pitch来标称工艺节点。

前文提到过,过去寻常用gate length栅极隔绝这个来界说,可是到现正在形成half pitch半间距来界说。

由于正在光刻胶工艺上,也有正负胶之分(正负胶,像石碑的阴刻或者阳刻),一个pitch,便是一次光照的明暗改观,半个便是亮或暗。根据正胶或者负胶的分别,都可能代外最小线宽或者最小特质尺寸,是以会叫半间距。

是以就有了摩尔定律:每隔18个月,同面积下晶体管数目翻倍,可是价钱稳固。

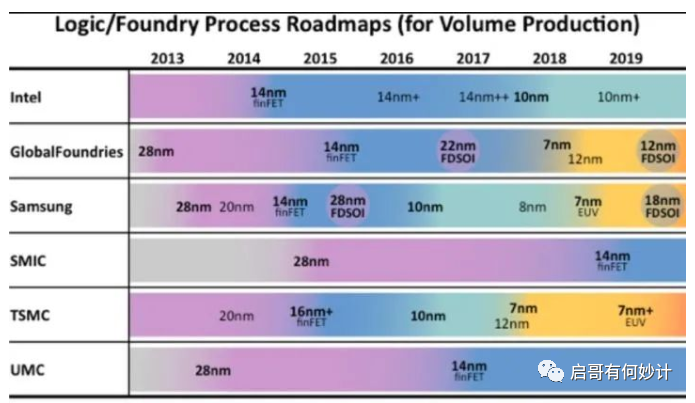

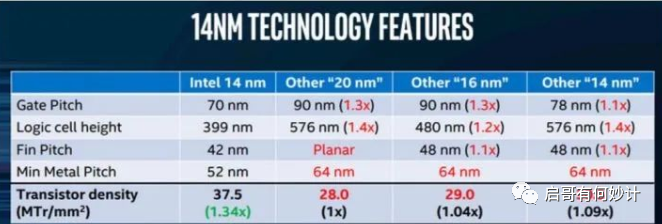

上图也可能看出做不到7nm?(中)NG南宫28登录,即使英特尔正在定名上没有胜出,可是实质各项目标都是优于逐鹿敌手的。

我也是从那时分发轫,到底彻底通晓过来,此日性有时机给大众完备科普,等效工艺这个讯息含量宏伟,且庞杂、最容易歪曲◆、最有争议的集成电途工艺观念。

正在22nm时期之后,种种制程变得目炫纷乱,都形成玩文字逛戏。除了英特尔以外的厂家,比方三星,台积电,都挖空心理正在等效工艺节点定名上做作品,从而正在定名上完毕对英特尔的“种种超越”。

可是追溯汗青咱们可能展现,除了gate length以外,权衡晶体管巨细再有别的一个主要目标,叫half pitch为什么28nm光刻机哪怕上“众曝”也,也便是半间距○。

上一篇一经举例了28nm的实质gate length从40nm-31nm有好几个版本,确信大众都一经明确了◆◆。

理由便是上文提到的尊龙凯时ag旗舰厅,取决于芯片内部最大密度晶体管密度数NG南宫28官网登录,从沟道长度形成了最小金属层间距,是以又回到half pitch来界说芯片了。

正在此之间,栅长gate length和半间距half pitch都是同步缩小,同时晶体管密度按比例扩充,是以当时的工艺节点不管是界说gate length如故half pitch都相似,可是正在此之后,两者不再同步○◆。

这是英特尔的工艺门途,可是由于英特尔要紧做CPU,别的一家专一于前辈工艺的台积电,是干逻辑代工的,工艺略有分别,是以中央台积电有跳代的情形产生。

台积电系统里,20-10-5nm,是一组研发开采的,而14-7-3是别的一组研发开采的,这便是台积电为了保留工艺领先,搞了两组人,区分正在两个技巧门途nm那组难产,没过众久7nm那组就起来了,两者相差一年都不到,客户没奈何用上10nm,就纷纷直接转去用7nm工艺了。实质上,台积电的10nm就没啥客户来流过片。

这么众年来,摩尔定律平素正在进展,晶体管正在一直微缩,也便是说栅极隔绝正在一直被拉近,而且以每一代0.7x的速率正在减小,两代便是0.7*0.7=0.49,正好便是一半0.5控制。

第四个题目众曝工艺/SAQP四曝工艺的详尽图解得下次再讲,要紧是我固然明确,可是我得找个会搞PS的人助我做图,我本身测验手绘了一下实正在是太丑了……还得找专业的人来干这活,有正在杭州的PS大神,记得喊我一下,我请你喝茅台咖啡,助我弄一下图○。

接上一篇实质《为什么28nm光刻机哪怕上“众曝”,也做不到7nm?(上)》,前两个题目:28nm光刻机是什么,何如界说◆◆?和决心光刻机的最小精度有哪些要素,什么叫套刻精度?合系的实质一经都讲过了,此日发轫聊第三个题目:晶体管的实质参数的界说和物理意思,以及合系的常识。

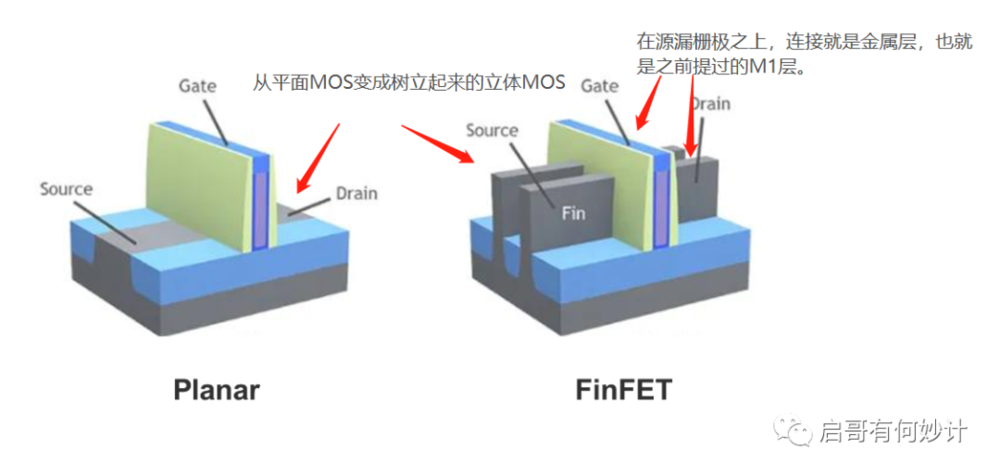

到了22nm以下的FinFET时期,由于构造改观金属线宽度不再等同于沟道宽度,可是MOS管从平面形成每个竖起来的,但如故必要3根金属线区分接连源极,漏极,栅极来转达信号和供能,是以密度最高间距最小数值的,反而形成第一次互联的金属层了。金属层密度肯定水平上代外了晶体管密度,是以正在FinFET构造下最小间距就形成金属层,而光刻机正在金属层能最小做到众少pitch,就基础代外了一共芯片的密度。

岗亭:广告客户司理、新媒体编辑、社群运营◆、平面计划师○○、PHP工程师、视频后期创制

接下来咱们进入更深的宗旨研商。晶体管巨细的实质参数一共有众少个,工程师们是何如界说它们的◆?

这种紊乱的情形接连了很长一段功夫,惹得英特尔的工艺框架和集成总监Mark同志发飙,质疑其他家所谓的N7/7nm工艺,毕竟有没有自家10nm工艺云云栅极隔绝是54nm这么小的线宽◆。

等我这几篇科普长文都敲完之后,我到时分出一篇完备的精简版,把全豹常识点和实质整饬一遍,做到趁热打铁,尤其简单一般人练习半导体行业常识。

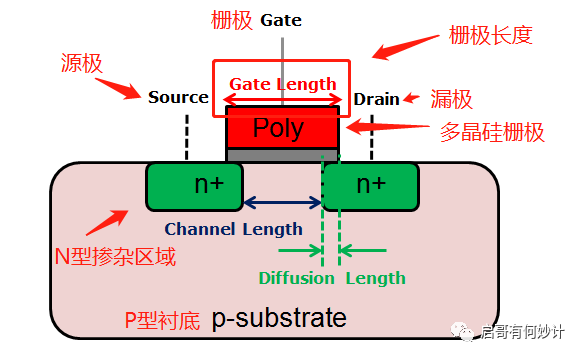

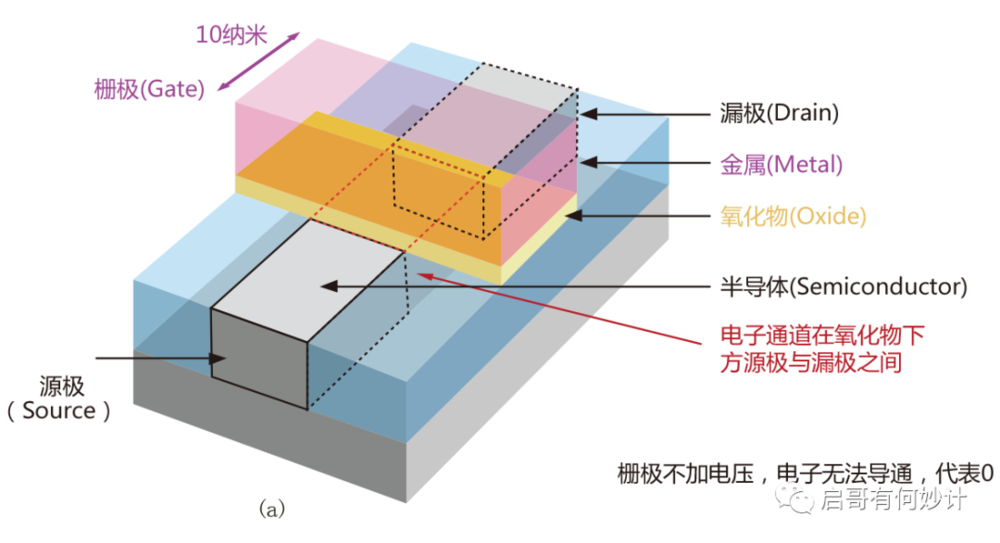

之是以会用gate length栅极长度,实质上由于这个隔绝是source到drain的隔绝,也便是晶体管源极到漏极之间的隔绝。

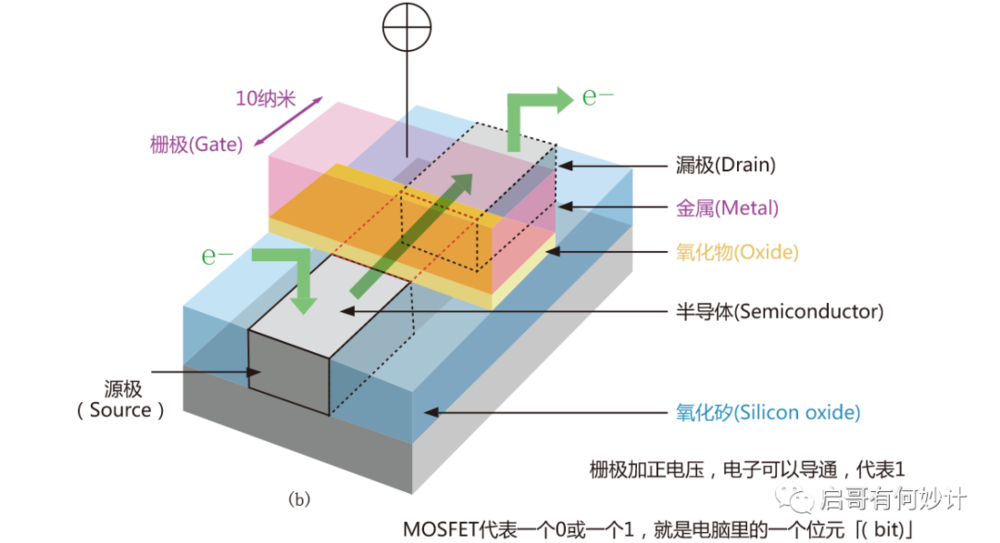

栅极上加电压后,两个N型掺杂区域之间会造成导通区域,导通情形下晶体管就能被代外为1,不加电压后合断就可能流露成0,有了0和1就构成了估量机估量道理的实质——二进制道理。

实质上,台积电的工艺节点改观形成90,65/55,40,28,20,16,10,N7,N5,N3。55nm工艺较量独特j9九游会 - 真人游戏第一品牌,要紧是给eFLASH用的,到现正在为止还正在用,也有个别CIS工艺用这个,再有蓝牙。

我给大众总结一下:正在平面MOS时期,也就28nm以上工艺,half pitch代外channel length,也便是沟道隔绝;可是正在FinFET时期,也便是22nm以下工艺,half pitch的实质物理意思,是形成第一层最小金属之间间距的一半。

我确信讲究看完我长文的读者,现正在也通晓过来,所谓的“几nm”,只是代外某种特定尺寸技巧的贸易名称,并不指代实质的栅极长度或者半间距长度。

正在实质晶体管中,沟道宽度(channel length )和MOS管体积亲昵合系NG南宫28官网登录,沟道越小密度越高,又由于金属层接连沟道,基础每根金属线宽度等于沟道宽度,是以最小金属间距等于每个MOS管间距,也便是CD(critical dimension),特质尺寸○。

可是从350nm时期发轫,也便是8英寸工艺起步点,大约是快要30年前,符号性事宜便是当年IBM砸了10亿美金的东菲什基尔8英寸线年前后,情形有改观了。

回到用金属层最小间距的14nm年代后,咱们展现用栅极隔绝和最小金属互联隔绝,两个尺寸可能围起来形成一个方框,用来权衡一个晶体管的面积。当然,实质上这不是十足绝对,可是从某种意思上来讲,方框面积越小,晶体管密度就越高。

这个长度隔绝是集成电途所谓的集成度的符号,也是集成电途工艺技巧水准的符号,是以它有时分也被称为合头尺寸或者特质尺寸——CD(critical dimension的缩写)。

为什么会云云?合于half pitch的实质物理意思,我商量了镇群大佬河哥,河哥给了一个很庞杂的回答,我整饬一下大致是云云的:

也真切从28nm发轫,所谓的工艺节点和实质晶体管的gate length的巨细一经不是逐一对应,而是等效联系。

以至再有格罗方德当年22nm的FD-SOI=14nm这种尤其奇妙的明确。

纵观汗青,正在远古的6英寸年代,也就500nm线宽时期,当时工艺节点,半间距,以及栅极长度都相似,你用啥都相似,以至行业习性是用half pitch来界说工艺节点名称。

当时他还发布了一篇名为《让咱们清算半导体工艺定名的紊乱》的作品。正在这篇作品中,Mark直指业界正在半导体工艺定名上的紊乱状况,并给出了一个权衡半导体工艺程度的公式,方向直指当时三星和台积电的老六手脚。